線上影音

Home > ANSYS SIwave 教學 > TDR Analysis

本文始於2009,2011、2019年修訂,旨在介紹TDR模擬。

-

SIwave Model Extraction

-

Designer TDR Analysis (v4以前舊法)

-

Designer TDR Analysis (目前版本方法)

-

問題與討論

5.2 為何TDR Probe看Open TDR結果很奇怪?

5.3 為何終端50歐姆的長走線,其TDR穩態結果會略高於50歐姆? (重要)

![]()

- SIwave Model Extraction

- Designer TDR Analysis (v4以前舊法)

-

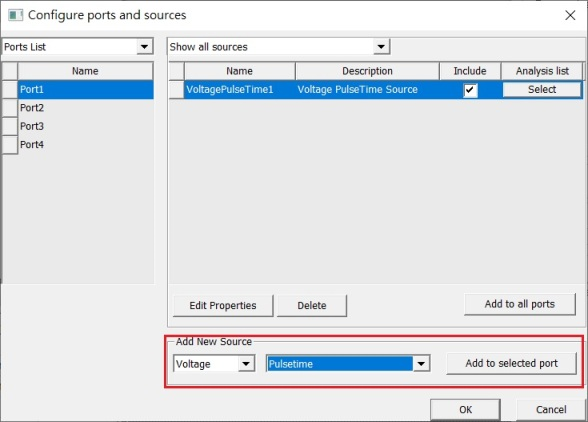

Voltage Source Type選"Pulsetime"

-

電壓振幅選1V(原因後述),tr,tf決定了TDR解析度,t(period)不可以小於w+tr+tf

- 都設定完成後按"OK"。

-

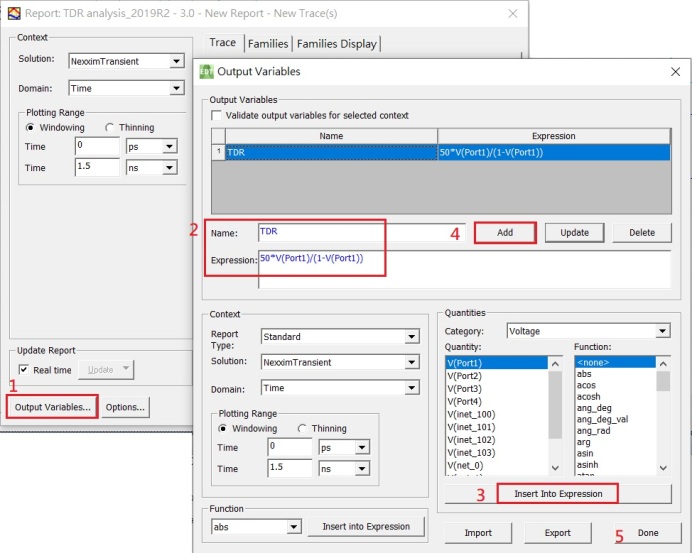

按"Output Variables"按鍵,跳出一個設定Output Variables的對話視窗

-

在Name任意輸入想要的output name,Expression則仿下輸入TDR公式:Zo = 50 * Vport / (1-Vport)

-

公式內的Vport變數,由右下方的Quantities框內的變數,選定後按"Insert Into Expression"

-

公式完成後,按"Add"就會加到最上方的公式列方框中

-

全部完成後,按"Down"

-

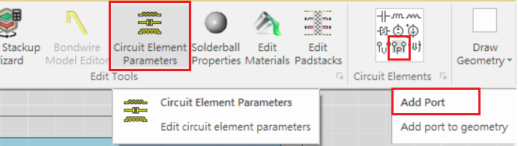

Designer TDR Analysis (目前版本方法)

-

問題與討論

- 參考文獻

TDR全名是"Time Domain Reflectometry",是量測高頻訊號在傳輸線的時域反射狀況,來判斷傳輸線特性阻抗的技術。[1]

TDR 曲線可以反應出傳輸線上寄生電容、寄生電感所引起的阻抗不連續性,而且這些寄生效應引發的TDR曲線的上升下降波形,可以轉換成等效電容、電感或其組合的模型,所以TDR也可以用來進行互連建模。[1]

2.1 Create PCB and

Trace model ![]()

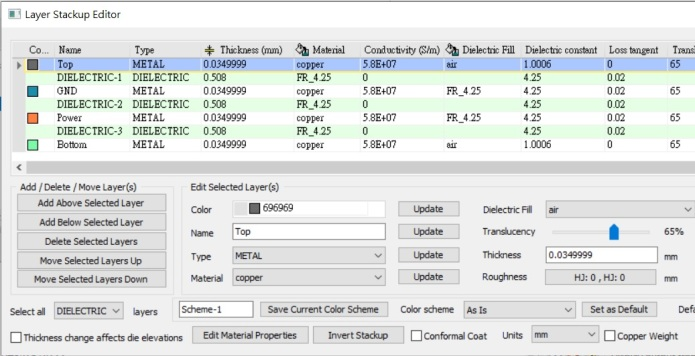

首先利用SIwave建一個四層板,FR4介電係數約4.25,總板厚約64mile

新增材質請從Edit \ Materials

新增或設定PCB堆疊請從Edit \ Layer Stack

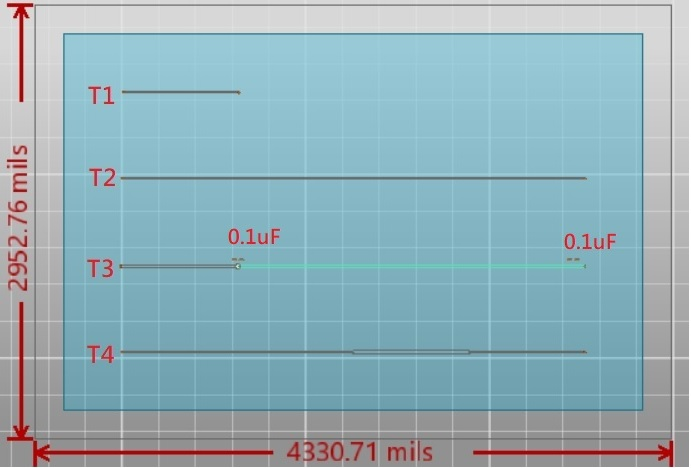

畫四條microstrip:

Trace1,線寬10mile,線長約20mm,net name [T1]

Trace2,線寬10mile,線長約80mm,net name [T2]

Trace3,線寬10mile,在線長20mm處,從top layer到bottom layer過孔換層,net name [T3]

Trace4,線寬10\5\20\10mile,每段線長約20mm,總線長80mm,net name [T4]

另外,在Via layer1 to layer4處,與Trace3右端附近,加一個bypass capacitor 0.1uF,以改善走線換層時的回流路徑不連續特性。

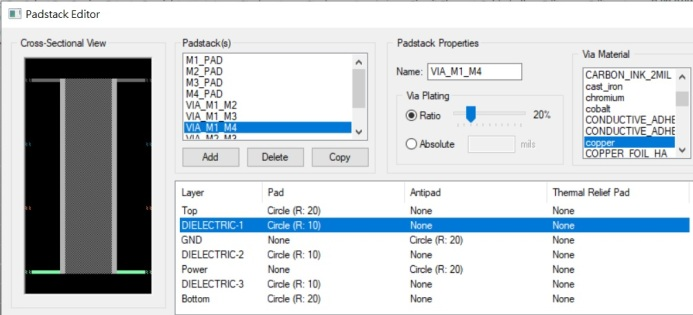

Trace3有從top layer轉到bottom layer的貫孔,此via的hole size radius=10mile、pad size radius=20mile、anti-pad radius=20mile

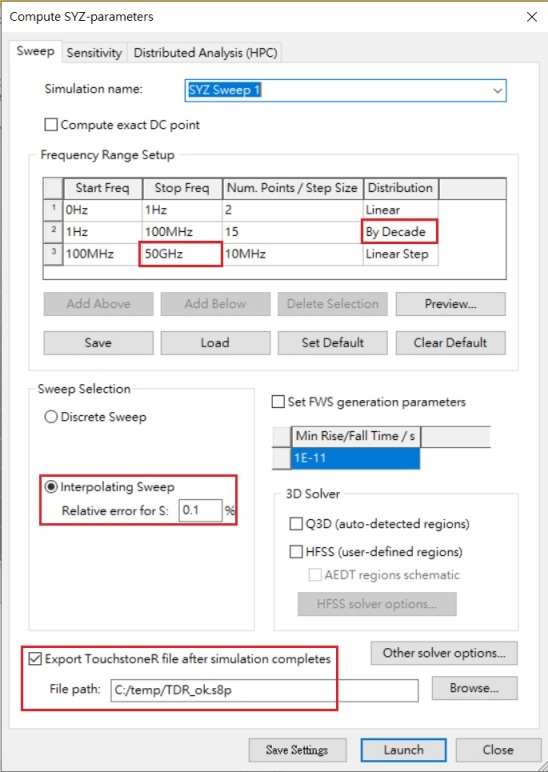

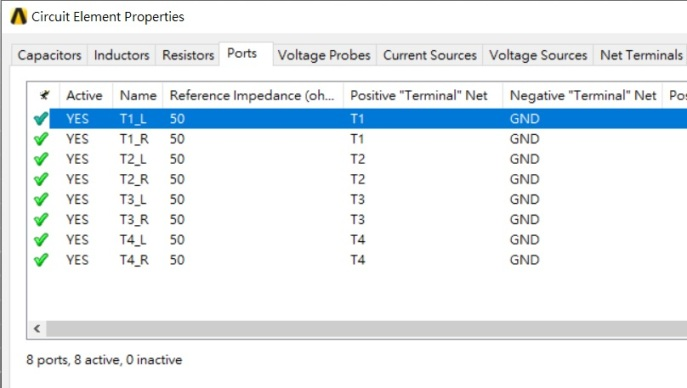

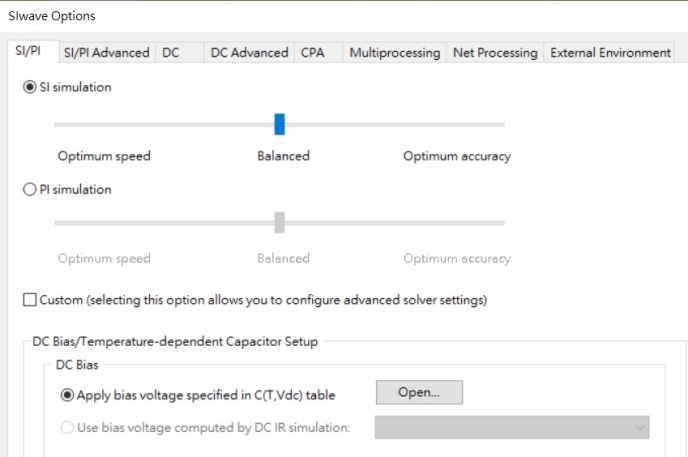

"Stop Freq/Hz"設的越大,代表所要模擬的頻寬越高("Min Rise/Fall Time/S"越小),SIwave做S-parameters模擬時切的mesh會越細,所花的模擬時間會增加。

做TDR分析時,因為看的訊號Rise Time較小,10ps(0.5/Tr=50GHz)~20ps(25GHz)~30ps(16GHz),所以"Stop Freq/Hz"、"Num Ponits"要設足夠,這樣跑出來的TDR解析度才夠。

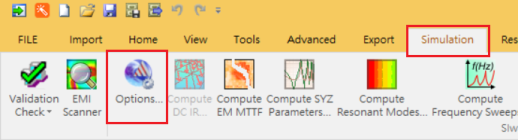

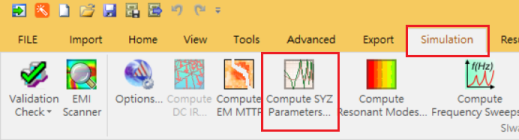

官方在Help內有提到,要看TDR,must perform an interpolating sweep。

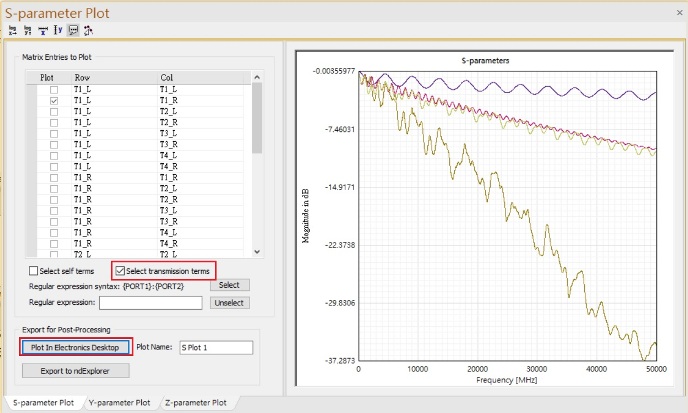

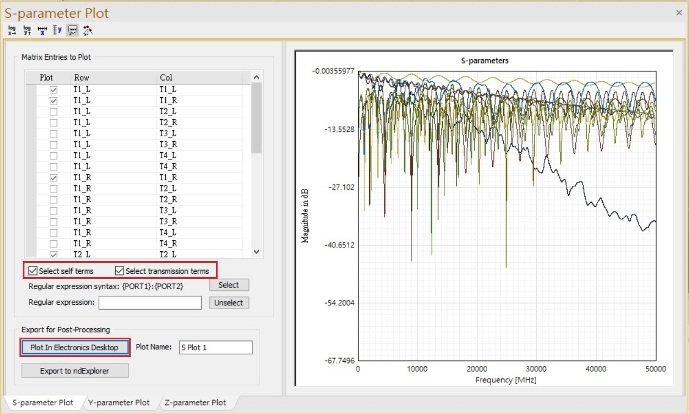

Results \ SYZ \ SYZ Sweep1 \ Plot Magnitude/Phase

上圖從SIwave6.0到SIwave 2019R2都一樣

預設顯示S21,您也可以勾選[Select self terms],就可以看S11。

按[Plot in electronics Desktop]

自SIwave 2014起,SIwave顯示時域波形的後處理介面與DesignerSI整合後,SIwave操作介面不再直接可以看TDR,必須如下第四節所示方法,進Designer環境透過TDR Probe看。

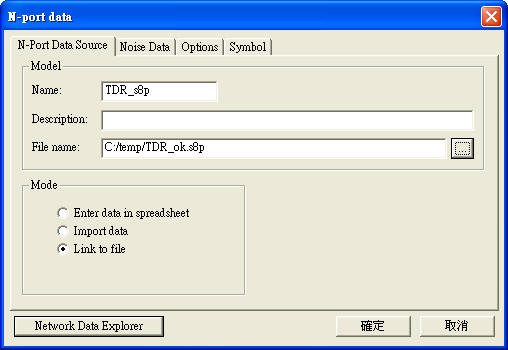

將step2所建四條傳輸線的S-parameter匯出成.s8p,再匯入Designer。詳細步驟可參閱"眼圖分析Add Nport Model"該章節。

在每一條Trace的左加端"Interface port",右端則加50歐姆的終端電阻。

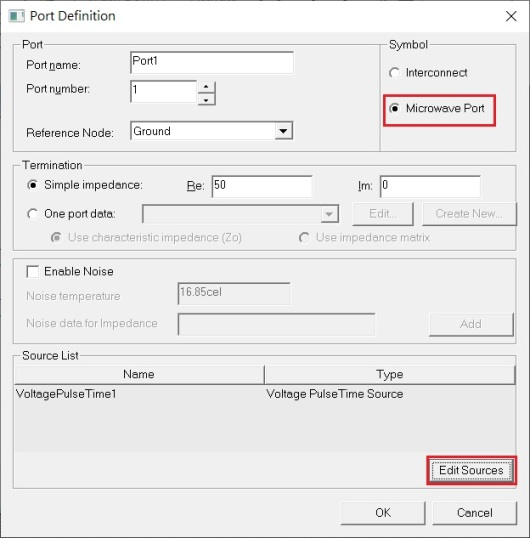

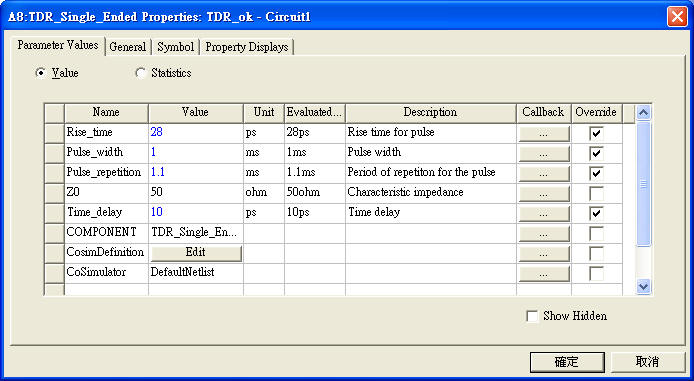

雙擊"Interface port",如下設定後,按"Edit Sources"添加Voltage Source

此時在上方視窗內,即可以看到新設置的VoltagePulseTime。

調整一下電路擺放位置

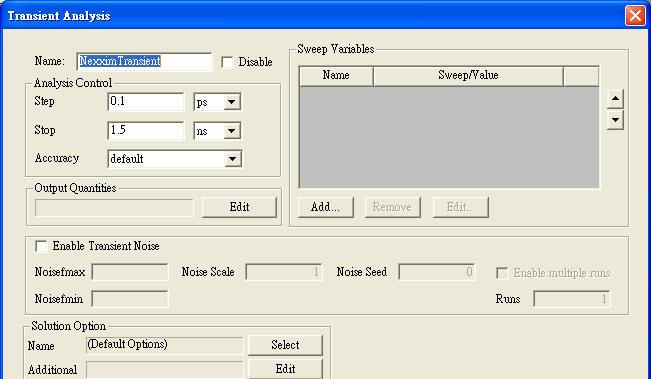

Add Transient Analysis" setting,然後按F10開始分析。>

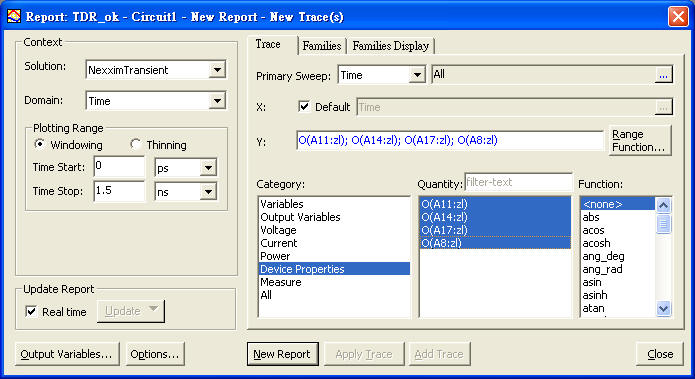

分析完成後,以滑鼠右鍵按Results \ Create Standard Report \ Rectangular Plot,出現"Report"對話框

這TDR輸出,從電壓轉電阻的公式算法是怎麼來的呢?

Vport = Vs * Zo / (Zo+Ro)

Zo = Ro * Vport / (Vs-Vport)

if Vs = 1V, Ro = 50 ohm

Then , Zo = 50 * Vport / (1-Vport)

在Output variables設定過TDR的輸出公式後,在Report設定視窗就可以看到TDR選項,選定後按"New Report"即可

![]() 通常我們看到TDR波形右邊是抬高衝上去的,那是因為待測Trace的

遠端是Open。本文跑出來波形右邊是收斂在50歐姆,是因為待測Trace終端50歐姆特性阻抗。至於為何不是每條線的穩態阻抗都收斂在50歐姆,請參考5.3

通常我們看到TDR波形右邊是抬高衝上去的,那是因為待測Trace的

遠端是Open。本文跑出來波形右邊是收斂在50歐姆,是因為待測Trace終端50歐姆特性阻抗。至於為何不是每條線的穩態阻抗都收斂在50歐姆,請參考5.3

4.1 Export Touch-Stone file (.snp) in SIwave

Results \ SYZ \ SYZ Sweep 1 \ Export to TouchstoneR File

4.2 Import Nport model in Designer

Project \ Add Model \ Add Nport Model

4.3 Add Single-Ended TDR source

Components tab \ Nexxim Circuit Elements \ Probs \ TDR_Single-Ended

4.4 Add Transient Analysis Setup

Circuit \ Add Nexxim Solution Setup \ Transient Analysis

4.5 Analyze and Report

5.1 介質參數如何影響TDR特性阻抗的變化? ![]()

Ans:

介質材料特性(Dk,Df)會影響TDR波形,但兩種參數影響TDR波形的物理機制不同 。

Dk透過電容(C=e*A/d)而直接影響特性阻抗(Zo=(L/C)^0.5)

Df影響的是TDR激發能量在傳遞過程中的(介質)損耗,同樣影響TDR結果

5.2 為何TDR Probe看Open TDR結果很奇怪? ![]()

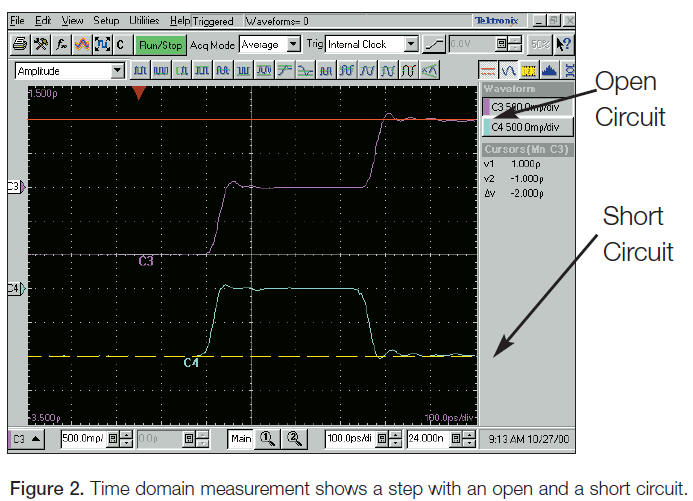

Ans:首先來看看, TDR with open terminal量測會看到什麼? [2] 請注意以下Y軸單位是 "電壓"

Designer TDR probe的結果,得到的Y軸單位則是 "電阻"(ohm),可參考本文第三章節所推導的公式Zo = 50*Vport/(1-Vport)

終端是50 ohm或short的結果沒有問題(Y軸單位ohm),但open的結果特別奇怪,雖然R19.x沒顯示單位,但點進去看Y軸單位是K ohm。(2019R1起Y軸會顯示單位)

當TDR終端open時,等於是要TDR probe在右端穩態畫出無限大的ohm,這造成上圖所示看到的奇怪結果。

TDR probe可以看terminal 50、short, 但如果要看終端open的條件,請適當調整X軸顯示的時間長度略大於兩倍傳輸線延遲即可(TDR反應時間)。

也可以透過V_Probe看電壓 (下圖Y軸單位是mV)

5.3 為何終端50歐姆的長走線,其TDR穩態結果會略高於50歐姆? ![]()

Ans: 這是常見的問題,本文step3與step4.5的TDR結果也可以看出這現象:雖然大家都終端50歐姆,但只有最短的T1走線最後穩態值是50歐姆,其他三條線都略大於50歐姆。這高出的數歐姆阻抗,是整個迴路的RDC所貢獻。早期的2010 siwave_gsg官方文件p.33就有說明,請參考本站另一篇文章。

還有一個很重要的現象是TDR masking effect[3]。假設有一由左至右分別是50ohm->80ohm->50ohm兩次阻抗不連續的"長"傳輸線,會發現TDR不論從左端打或從右端打入,近端TDR都能看到50ohm,但遠端的TDR都不會是50ohm。這是因為TDR的激發能量(上升緣),在第一次遇到阻抗不連續就部分反彈了,導致在遇到第二次不連續時,上升緣變緩不足以反映真實的TDR準度。

5.4 TDR除了用來觀察傳輸線特性阻抗,還可以有什麼其他用途? ![]()

Ans: Eric Bogatin在DesignCon 2022介紹一種以TDR推等效介電常數的方法[6]

Co:真空的光速

L:上圖傳輸線上兩個不連續節點的間的距離

5.5 如果HFSS內直接看TDR,跟Designer內看TDR的結果不同,是什麼原因? ![]()

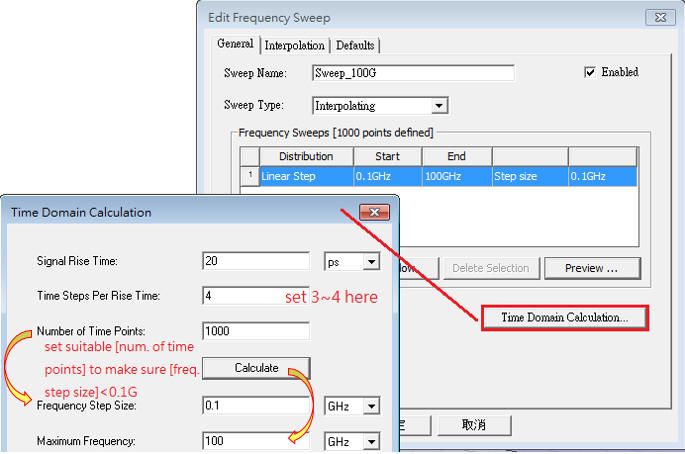

Ans: 這是使用者常問的問題,主要原因在於不知道HFSS與Designer計算TDR採用的技術不同,如果是用HFSS直接看TDR,那model extraction的有效頻寬要是原本的3~4倍。

舉例來說,若取Tr of Rising edge =20ps透過Designer觀察TDR,那Designer所使用的SNP model(S-parameter model)萃取時取0.5/Tr=25GHz的頻寬即可得到理想的結果。但如果同樣的題目想直接在HFSS內看TDR,由於HFSS並不是像Designer直接打step function透過暫態分析得到TDR,而是透過IFFT(反快速傅立葉轉換)得到TDR,所以此時的取樣頻點要夠多結果才會正確,一般建議Tr的時間寬度內至少有3~4個取樣頻點, 整個掃頻的頻寬取75~100G,如下圖所示。

為了節省模擬時間,一般建議透過Designer看TDR。

在Designer內看TDR時,待測物模型的萃取頻寬只要大於0.5/Tr,結果會是幾乎一樣的。也就是只要模型的頻寬夠,固定Tr下看到的TDR是相同的。但在HFSS內看TDR時,待測物模型的萃取頻寬取0.5/Tr與4*0.5/Tr,即使Tr固定,一些例子會發現結果有明顯差異。另外,在Designer內以TDR source激發TDR波形時(如step4.3)必須注意相鄰線間是否有NEXT/FEXT耦合,如果有,TDR就要分開激發不能同時激發。

[1] All about TDR by Tektronix, p.25, 28

[2] TDR Impedance Measurements: A Foundation for Signal Integrity, p.3

[3] TDR Masking Effect, p.24

[4] Designer"Circuit Design -- Time Domain Reflection" by Ansoft.

[5] Altera "Guidelines for Designing High-Speed FPGA PCBs" at p.2~7 introduce TDR and estimate LC effect.

[6] Eric Bogatin, "Three Very Low Cost Technology Solutions for SI Applications", DesignCon2022.